## Лекция 28

# ЭЛЕМЕНТЫ ЦИФРОВОЙ ЭЛЕКТРОНИКИ

#### План

- 1. Базовые логические элементы.

- 2. Логический инвертор.

- 3. Логический инвертор на биполярном транзисторе.

- 4. КМОП-инвертор.

- 5. Выводы.

### 1. Базовые логические элементы

Функционирование устройств цифровой электроники проходит в двоичной системе счисления, оперирующей двумя цифрами: нуль (0) и единица (1). Математическим аппаратом, на основе которого реализуются цифровые устройства, является алгебра логики.

Основные операции алгебры логики – логическое сложение, логическое умножение и логическое отрицание.

*Логическое сложение* (операция ИЛИ): F = A + B, читается «А или В». Эта операция означает, что сложное высказывание истинно, если истинно хотя бы одно из простых высказываний или истинны оба высказывания. Операцию логического сложения называют *дизъюнкцией*.

Логическое умножение (операция И): F = A \* B, читается «А и В» Эта операция означает, что сложное высказывание истинно лишь тогда, когда истинны все простые высказывания. Операцию логического умножения называют конъюнкцией.

Логическое отрицание (операция НЕ, *погическое отрицание*):  $F = \overline{A}$ , читается «не A ». Эта операция означает, что результирующее высказывание истинно, если исходное ложно, и наоборот.

Основные логические функции могут быть реализованы с помощью электронных схем, называемых *погическими элементами*. Эти схемы имеют один или несколько входов и, как правило, один выход. Уровень напряжения на выходе логической схемы определяется уровнями напряжения на входах и характером реализуемой логической функции.

С помощью элементов, реализующих логические функции И, ИЛИ, НЕ можно создать цифровую схему, осуществляющую сколь угодно сложную логическую операцию. Поэтому такие элементы называют *базовыми*.

Существует множество базовых логических элементов, различающихся схемотехнической реализацией, конструкцией и технологией изготовления,

напряжением питания, быстродействием, потребляемой мощностью и другими параметрами. В интегральной схемотехнике используют элементы И-НЕ, а также ИЛИ-НЕ. Каждый из этих элементов позволяет реализовать все виды логических операций. Например, элемент НЕ легко получается как из элемента ИЛИ-НЕ, так и из элемента И-НЕ параллельным соединением входов.

На различных этапах развития цифровой техники использовались резистивно-транзисторная логика (РТЛ), диодно-транзисторная логика (ДТЛ), транзисторно-транзисторная логика (ТТЛ), эмиттерно-связанная логика (ЭСЛ), логика на МОП-транзисторах и т. д. Логики РТЛ и ДТЛ в настоящее время не применяются. Элементы ТТЛ-логики широко использовались в микросхемах малой и средней степени интеграции в 70–80 годы XX в. Значительное распространение они имеют и теперь. Однако при построении современных цифровых систем большой и сверхбольшой степени интеграции (БИС и СБИС) доминирующей является КМОП-логика. Перспективными являются логические элементы на совмещенных биполярных и МОП-транзисторах — БиКМОП-логика. В таких элементах сочетаются преимущества биполярных и МОП-технологий.

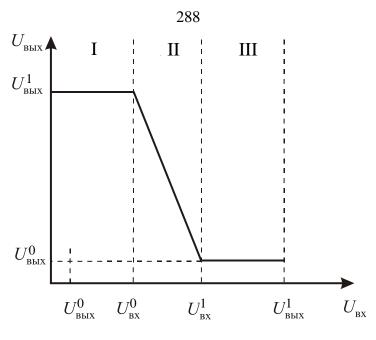

## 2. Логический инвертор

Инвертор реализует функцию НЕ и является простейшим базовым логическим элементом. Свойства инвертора характеризует его передаточная характеристика  $U_{\rm вых}=f(U_{\rm вx})$ , представляющая зависимость выходного напряжения  $U_{\rm вых}$  от медленно изменяющегося напряжения на входе  $U_{\rm вx}$ . Передаточная характеристика инвертора показана на рис. 28.1.1. Высокий уровень напряжения соответствует логической единице, а низкий – логическому нулю.

Передаточная характеристика инвертора на рис. 28.1 имеет три области. Область I соответствует логической единице на выходе, область III – логическому нулю. Область II является переходной. В этой области инвертор работает как усилитель.

Высокий уровень напряжения на выходе инвертора не зависит от точного значения входного напряжения, пока последнее не превысит величину  $U_{\rm BX}^0$ . Таким образом,  $U_{\rm BX}^0$  — это максимальное значение входного напряжения, соответствующее логическому нулю. Точно так же низкий уровень выходного напряжения не зависит от величины входного напряжения, если оно остается больше величины  $U_{\rm BX}^1$ . Следовательно,  $U_{\rm BX}^1$  — это минимальное значение входного напряжения, соответствующее логической единице.

Рис. 28.1

# 3. Инвертор на биполярном транзисторе

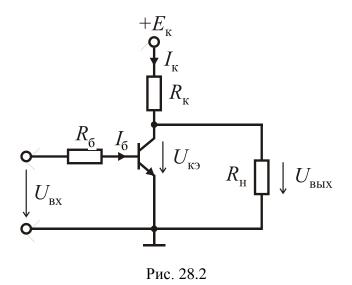

Простейший инвертор на биполярном транзисторе показан на рис. 28.2. Резистор  $R_6$  в цепи базы служит для задания необходимого тока базы. Резистор  $R_{\rm K}$  является внутренней нагрузкой инвертора, а резистор  $R_{\rm H}$  — его внешней нагрузкой. Величина внешней нагрузки может меняться в широких пределах. При  $R_{\rm K}=\infty$  инвертор работает в режиме холостого хода. Предельной нагрузкой, при которой инвертор еще должен сохранять свои параметры, считают величину  $R_{\rm K}=R_{\rm H}$ .

Рассмотрим статический (по постоянному току) и динамический режимы работы инвертора.

*Статический режим.* В статическом режиме логический инвертор может быть закрыт (транзистор находится в режиме отсечки) либо открыт (транзистор находится в режиме насыщения). Инвертор закрыт, когда напряжение на входе меньше напряжения логического нуля  $U_{\rm BX}^0$ . Для инверторов на кремниевых биполярных транзисторах оно составляет 0.4-0.5 В. В этом режиме  $I_{\rm K}=I_{\rm G}\approx 0$ ,  $U_{\rm K9}=E_{\rm K}-R_{\rm K}I_{\rm K}\approx E_{\rm K}$ . Сопротивление закрытого инвертора составляет сотни кОм.

Если на входе действует импульс напряжения такой величины, чтобы транзистор находился в режиме насыщения, то ток базы

$$I_{\rm G} = \frac{U_{\rm BX} - U_{\rm G9}}{R_{\rm G}} \approx \frac{U_{\rm BX}}{R_{\rm G}}.$$

В режиме насыщения оба перехода смещены в прямом направлении, и ток коллектора возрастает до наибольшего значения:

$$I_{\scriptscriptstyle \mathrm{K}} = I_{\scriptscriptstyle \mathrm{KHac}} = \frac{E_{\scriptscriptstyle \mathrm{K}} - U_{\scriptscriptstyle \mathrm{K}9}}{R_{\scriptscriptstyle \mathrm{K}}} pprox \frac{E_{\scriptscriptstyle \mathrm{K}}}{R_{\scriptscriptstyle \mathrm{K}}} \, .$$

Напряжение  $U_{\kappa_9}$  в режиме насыщения составляет 0.2–0.3 В, а выходное сопротивление — несколько десятков Ом. Для насыщения транзистора необходимо, чтобы ток базы стал больше минимального значения, при котором начинается насыщение транзистора:

$$I_{\rm f} > \frac{I_{\rm KHaC}}{\beta} \approx \frac{E_{\rm K}}{\beta R_{\rm K}}$$

.

Глубину насыщения транзистора характеризуют коэффициентом (степенью) насыщения, который определяет, во сколько раз реальный ток базы превосходит минимальное значение, при котором имеет место режим насыщения:

$$S = \frac{I_{6}}{I_{6 \text{ mag}}}.$$

Величину коэффициента насыщения выбирают от 1.5 до 3.

Транзистор должен входить в режим насыщения, когда входное напряжение превышает напряжение логической единицы  $U_{\rm Bx}^1$ . Для инверторов на биполярных транзисторах  $U_{\rm Bx}^1 \approx 1.5~{\rm B}$ .

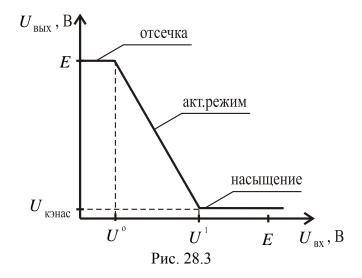

Передаточная характеристика инвертора на БТ показана на рис. 28.3. Рабочими являются участки переходной характеристики, соответствующие отсечке и насыщению.

**Динамический режим работы инвертора**. Переходные процессы в инверторе на биполярном транзисторе определяются следующими причинами.

- 1. Наличием емкостей эмиттерного и коллекторного переходов. При переключениях происходит заряд и разряд этих емкостей.

- 2. Накоплением и рассасыванием неосновных носителей в базе при переходе транзистора в режимы насыщения и отсечки.

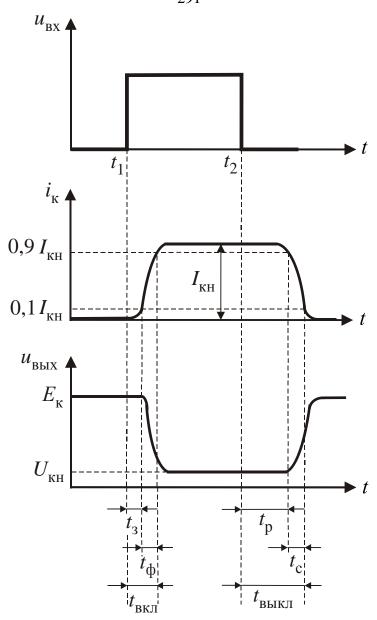

Рассмотрим упрощенно процессы в транзисторе при действии на входе прямоугольного импульса (рис. 28.4). На интервале времени  $0-t_1$  инвертор закрыт. Процесс открывания инвертора после подачи входного импульса можно разделить на три этапа: задержка фронта, формирование фронта и накопление избыточного заряда в базе.

3aдержка фронта коллекторного тока  $t_3$  — это интервал времени между моментом начала действия импульса и моментом, когда ток коллектора достигает значения, равного  $0.1I_{\rm khac}$ . Задержка фронта обусловлена зарядом барьерной емкости эмиттерного перехода.

С момента начала отпирания транзистора начинается формирование фронта выходного импульса (интервал  $t_{\phi}$  на рис. 28.4). Когда ток коллектора достигает уровня  $I_{\kappa \text{нас}}$ , напряжение на коллекторе уменьшается до величины  $U_{\kappa \text{энас}}$ . Ток базы достигает величины  $I_{\text{бнас}}$  и продолжает увеличиваться, а в базе происходит накопление неосновных носителей.

Общее *время включения*  $t_{\text{вкл}}$  складывается из времени задержки и длительности фронта:

$$t_{\rm вкл} = t_{\rm 3} + t_{\rm ф}.$$

Рис. 28.4

После окончания действия входного импульса начинается рассасывание избыточного заряда в базе. За счет этого коллекторный ток не меняется в течение времени  $t_{\rm P}$ . Затем начинается спад коллекторного тока. Одновременно растет напряжение коллектора. Общая длительность выключения

$$t_{\text{выкл}} = t_{\text{P}} + t_{\text{c}}$$

.

Здесь  $t_{\rm c}$  – время спада коллекторного тока.

Основным фактором, ограничивающим быстродействие инвертора на рис. 28.2, является насыщение транзистора. Время рассасывания  $t_{\rm P}$  существенно превышает остальные временные интервалы.

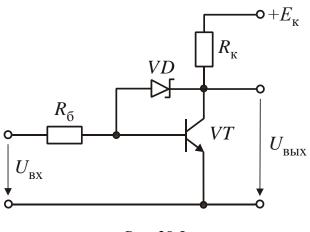

Для исключения глубокого насыщения транзистора коллекторный переход шунтируют диодом Шоттки (рис. 28.5), имеющим малое время переключения, низкое напряжение отпирания (0.2–0.3 В) и малое сопротивление в открытом состоянии.

Рис. 28.5

Когда транзистор открыт и находится в активном режиме, напряжение коллектор-база положительно ( $U_{\rm ko}>0$ ), и к диоду приложено обратное напряжение. С ростом коллекторного тока напряжение на коллекторном переходе уменьшается и диод открывается. Последующее увеличение тока базы приводит к увеличению тока через диод. Поскольку напряжение отпирания диода Шоттки меньше напряжения отпирания коллекторного перехода, последний остается закрытым и накопление неосновных носителей в базе транзистора не происходит.

Таким образом, увеличение быстродействия инвертора с диодом Шоттки происходит в основном за счет уменьшения времени рассасывания при выключении. Выходное напряжение такого инвертора в открытом состоянии больше, чем напряжение транзистора в режиме насыщения.

Изготавливаются диоды Шоттки на общем кристалле одновременно с остальными элементами в едином технологическом процессе. Транзисторы с диодами Шоттки часто называют *транзисторами с барьером Шоттки* или *транзисторами Шоттки*.

# 4. Инвертор на КМОП-транзисторах (КМОП-инвертор)

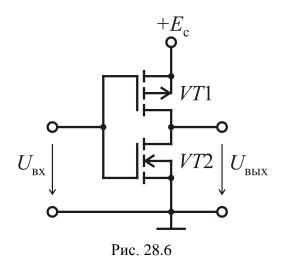

Инвертор с минимальным потреблением мощности можно реализовать на комплементарной (дополняющей) паре полевых транзисторов (рис. 28.6). В такой схеме используются два МОП-транзистора с индуцированными каналами *n*- и *p*-типов. Подложки обоих транзисторов соединены с истоками.

*Статический режим работы КМОП-инвертора*. Если входное напряжение равно нулю, то транзистор VT2 находится в состоянии отсечки.

Напряжение затвора p-канального транзистора VT1 равно  $-E_c$ , напряжение  $U_{\rm cul} \approx 0$ , и он находится в линейном режиме. Таким образом, при  $U_{\rm BX} = 0$  выходное напряжение  $U_{\rm BMX} \approx E_c$ .

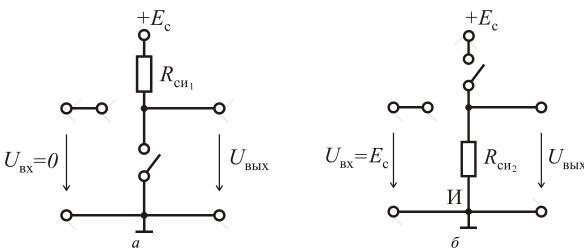

Эквивалентная схема КМОП-инвертора, соответствующая случаю, когда входное напряжение имеет низкий уровень, показана на рис. 28.7, a. Транзистор VT2 эквивалентен разомкнутому идеальному ключу. Ненулевое сопротивление VT1 моделируется резистором  $R_{\rm cul}$ . Его сопротивление

$$R_{\rm cul} = \frac{1}{b_1 (E_{\rm c} - U_{01})}.$$

Если входное напряжение имеет высокий уровень  $U_{\rm вx}>U_0$ , то транзистор VT2 находится в состоянии насыщения, а VT1 — отсечки, и выходное напряжение не превышает  $10~{\rm mB}$ . Эквивалентная схема инвертора для этого случая показана на рис.  $28.7,~\delta$ . Теперь транзистор VT1 эквивалентен разомкнутому ключу, а ненулевое сопротивление VT2 моделируется резистором  $R_{\rm cu2}$ , сопротивление которого

$$R_{\text{\tiny CM2}} = \frac{1}{b_2 (E_{\text{\tiny c}} - U_{02})}.$$

Транзисторы в схеме инвертора рассчитывают так, чтобы они были согласованы, т. е. имели одинаковые (по модулю) пороговые напряжения и удельные проводимости:

$$|U_{01}| = U_{02},$$

$$b_1 = b_2 = b.$$

Рис. 28.7

Этим обеспечивается одинаковая нагрузочная способность инвертора как в открытом, так и в закрытом состояниях. Поскольку приповерхностная подвижность дырок  $\mu_p$  в 2–4 раза меньше подвижности электронов  $\mu_n$ , для согласования ширину канала транзистора VT1 выбирают в 2–4 раза большей, чем у VT2. Длина каналов обоих транзисторов одинакова, а ширину выбирают так, чтобы выполнялось равенство

$$\frac{W_p}{W_n} = \frac{\mu_n}{\mu_n}.$$

**Динамический режим работы КМОП-инвертора**. Переходные процессы в МОП-инверторах обусловлены в основном перезарядом емкостей, входящих в состав нагрузки. Типичные значения суммарной емкости у инверторов, использующих транзисторы с длиной канала менее 1 мкм, не превышают 1 пФ.

Заряд емкости происходит через открытый транзистор VT1 при закрытом VT2, а разряд — через VT2 при закрытом VT1. Если транзисторы согласованы, т. е. их удельные проводимости одинаковы, длительность переходных процессов в обоих случаях примерно равна.

Время переключения схемы из состояния логической единицы в состояние логического нуля определяют с помощью приближенного равенства

$$t_{10} \approx \frac{1.6C_{_{\rm H}}}{bE_{_{\rm C}}}.$$

(28.1)

Полученное выражение является приближенным. Его значение состоит в первую очередь в том, что оно позволяет оценивать влияние параметров цепи на время переключения. Если транзисторы в схеме инвертора согласо-

ваны, то время переключения из состояния логического нуля в состояние логической единицы  $t_{01}$  также определяется формулой (28.1).

Из (28.1) следует, что для уменьшения времени переключения необходимо уменьшить суммарную емкость и увеличить напряжение питания  $E_c$ . Однако при увеличении  $E_c$  растет и мощность, потребляемая инвертором. Поэтому главный путь увеличения быстродействия – уменьшение емкости  $C_{\rm H}$ .

Перечислим основные свойства КМОП-инвертора.

1. В обоих состояниях инвертора один из транзисторов заперт, поэтому ток в цепи между источником и землей ничтожно мал, и в статическом режиме схема практически не потребляет мощность от источника питания. Динамические потери, т. е. мощность, рассеиваемая КМОП-инвертором при тактовой частоте f, определяются формулой

$$P_d = fCE^2$$

.

Из последнего равенства следует, что для уменьшения динамических потерь необходимо уменьшать емкость нагрузки и напряжение питания схемы. Однако уменьшение напряжения приводит к снижению быстродействия. Поэтому главным путем повышения быстродействия и снижения потерь является уменьшение емкостей транзисторов и нагрузки.

- 2. В обоих статических состояниях выход схемы подключен к общей шине или источнику питания через небольшие сопротивления каналов открытых транзисторов. Поэтому выходное напряжение равно нулю или напряжению питания и почти не зависит от параметров транзисторов.

- 3. Разность выходных напряжений инвертора в закрытом и открытом состояниях максимальна (близка к величине напряжения питания E). Это обеспечивает высокую помехоустойчивость схемы.

- 4. КМОП-инверторы обладают значительно большей нагрузочной способностью, чем инверторы на биполярных транзисторах. Входное сопротивление МОП-ттранзиистора бесконечно велико. Поэтому к его выходу можно подключить большое число аналогичных инверторов. При этом уровень выходного напряжения практически не изменится. Однако каждый дополнительный инвертор увеличивает емкость нагрузки, что приводит к замедлению переключения инвертора из одного логического состояния в другое.

КМОП-инвертор является практически идеальным логическим инвертором. Его быстродействие оказывается значительно выше, чем у других типов инверторов. Совершенствование технологии производства КМОП-интегральных схем привело к тому, что в настоящее время они стали доминирующими при производстве цифровых схем не только высокой, но и средней степени интеграции.

### 5. Выводы

- 1. Функционирование устройств цифровой электроники проходит в двоичной системе счисления. Математическим аппаратом, на основе которого реализуются цифровые устройства, является алгебра логики.

- 2. Основные логические функции могут быть реализованы с помощью электронных схем, называемых логическими элементами. Эти схемы имеют один или несколько входов и, как правило, один выход. Уровень напряжения на выходе логической схемы определяется уровнями напряжения на входах и характером реализуемой логической функции.

- 3. С помощью базовых логических элементов, реализующих функции И, ИЛИ, НЕ можно создать цифровую схему, осуществляющую сколь угодно сложную логическую операцию.

- 4. КМОП-инвертор является практически идеальным логическим инвертором. Его быстродействие оказывается значительно выше, чем у других типов инверторов.