Дифференциальный усилитель на МОП-транзисторах

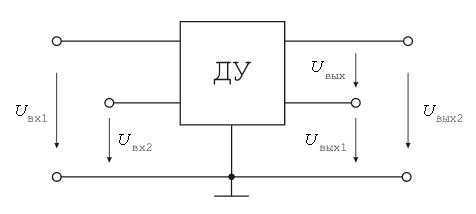

В современной радиоэлектронике широкое применение находят дифференциальные (разностные) усилители. Дифференциальный усилитель (ДУ) представляет симметричную схему с двумя входами и двумя выходами (рис. 4.2.1). Вход, обозначенный символом «+», называют неинвертирующим. Вход, обозначенный символом «–», называют инвертирующим. Поскольку схема имеет два выхода, в качестве выходного можно использовать напряжения ![]() ,

, ![]() или их разность

или их разность ![]() . В последнем случае выход дифференциального усилителя называют симметричным.

. В последнем случае выход дифференциального усилителя называют симметричным.

Рис. 4.2.1

Сигналы на входе дифференциального усилителя представляют в виде суммы дифференциальной и синфазной составляющих:

![]() ;

;

![]() .

.

Из последних равенств следует, что дифференциальный сигнал равен разности входных напряжений:

![]() , (4.2.1)

, (4.2.1)

а синфазный – их полусумме:

![]() . (4.2.2)

. (4.2.2)

В соответствии с (4.2.1) и (4.2.2) источник сигнала на входе дифференциального усилителя можно представить эквивалентной схемой, показанной на рис. 4.2.2.

Рис. 4.2.2

Различают коэффициенты усиления дифференциального и синфазного сигналов:

;

;

.

.

Важное свойство дифференциального усилителя заключается в том, что он усиливает дифференциальные и ослабляет синфазные составляющие сигнала. Одним из главных параметров дифференциального усилителя является коэффициент ослабления синфазного сигнала, который показывает, во сколько раз коэффициент усиления дифференциального сигнала больше коэффициента синфазного сигнала:

.

.

Дифференциальные усилители находят широкое применение в аналоговых интегральных схемах: операционных усилителях, аналоговых перемножителях, компараторах и т. д. Это объясняется следующими причинами.

Схема дифференциального усилителя на МОП-транзисторах показана на рис. 4.2.3. Смещение рабочих точек обоих транзисторов создается источником тока J. Как правило, источник тока реализуется на основе токового зеркала.

Рис. 4.2.3

Схема усилителя на рис. 4.2.3 имеет два плеча. Первое плечо образовано резистором ![]() и транзистором VT1, а второе – резистором

и транзистором VT1, а второе – резистором ![]() и транзистором VT2. Будем считать, что характеристики обоих плеч идентичны: параметры обоих транзисторов одинаковы, а

и транзистором VT2. Будем считать, что характеристики обоих плеч идентичны: параметры обоих транзисторов одинаковы, а ![]() . На практике это легко достигается в интегральных схемах, когда все элементы расположены на одном кристалле.

. На практике это легко достигается в интегральных схемах, когда все элементы расположены на одном кристалле.

Если схема на рис. 4.2.3 симметрична, усиление синфазного сигнала не происходит. ДУ усиливает только дифференциальные составляющие сигнала и подавляет синфазный сигнал.

Пример 4.1. Расчет ДУ в режиме постоянного тока. В схеме дифференциального усилителя на рис. 4.2.3 ![]() ,

, ![]() ,

, ![]() . Параметры транзисторов одинаковы: пороговое напряжение

. Параметры транзисторов одинаковы: пороговое напряжение ![]() , удельная проводимость

, удельная проводимость ![]() . Определить токи

. Определить токи ![]() и

и ![]() , напряжения затвор-исток и выходные напряжения для двух случаев:

, напряжения затвор-исток и выходные напряжения для двух случаев:

Решение. Случай 1. Поскольку плечи схемы симметричны и входные напряжения одинаковы, ток источника ![]() делится пополам, т. е.

делится пополам, т. е. ![]() . Напряжения затвор-исток также одинаковы:

. Напряжения затвор-исток также одинаковы:

![]() .

.

Выходные напряжения ![]() .

.

Напряжения истоков ![]() .

.

Случай 2. Поскольку входные напряжения одинаковы, токи стока остаются прежними:![]() . Не изменятся напряжения затвор-исток, а также выходные напряжения:

. Не изменятся напряжения затвор-исток, а также выходные напряжения: ![]() ;

; ![]()

![]() . Изменятся только напряжения истоков:

. Изменятся только напряжения истоков: ![]()

![]() .

.

Приведем расчетные соотношения для определения коэффициентов усиления дифференциальной и синфазной составляющих переменного сигнала в схеме на рис. 4.2.3.

Коэффициент усиления дифференциального сигнала. Если дифференциальная составляющая сигнала мала, транзисторы можно заменить схемами замещения для режима малого сигнала. В этом случае выходные напряжения

![]() ;

;

![]() ;

;

Здесь ![]() – удельная проводимость МОП-транзистора, определяемая формулой

– удельная проводимость МОП-транзистора, определяемая формулой

![]() .

.

Если используется симметричный выход, то

![]() .

.

Итак, коэффициент усиления дифференциального сигнала:

.

.

Если используется симметричный выход, то коэффициент усиления окажется в два раза выше:

![]() .

.

Коэффициент усиления синфазного сигнала

Выходные напряжения, обусловленные синфазной составляющей сигнала,

(4.2.5)

(4.2.5)

Коэффициент усиления синфазного сигнала

(4.2.6)

(4.2.6)

Поскольку внутреннее сопротивление источника тока значительно больше сопротивления резистора в цепи стока, коэффициент усиления синфазного сигнала очень мал.

Если напряжение снимается с симметричного выхода, то

![]()

Таким образом, если используется симметричный выход, коэффициент усиления синфазного сигнала ![]() .

.

Коэффициент ослабления синфазного сигнала

(4.2.7)

(4.2.7)

В случае симметричного выхода ![]() .

.

Коэффициент ослабления синфазного сигнала находится в прямой зависимости от сопротивления источника тока. Для увеличения ![]() его сопротивление должно быть как можно больше.

его сопротивление должно быть как можно больше.

В реальных устройствах невозможно добиться полной симметрии плеч дифференциального усилителя. Поэтому степень подавления синфазного сигнала не столь велика. Коэффициент ослабления синфазного сигнала высококачественных усилителей составляет 104–105. Обычно ![]() выражают в децибелах. Коэффициент ослабления синфазной составляющей современных дифференциальных усилителей составляет 80–100 дБ.

выражают в децибелах. Коэффициент ослабления синфазной составляющей современных дифференциальных усилителей составляет 80–100 дБ.

Пример 4.2. Расчет параметров ДУ. Рассчитать параметры дифференциального усилителя, показанного на рис. 4.2.3. Сопротивление резисторов в цепи стоков ![]() . Удельная проводимость транзисторов

. Удельная проводимость транзисторов ![]() . Ток источника

. Ток источника ![]() , внутреннее сопротивление

, внутреннее сопротивление ![]() .

.

Решение. Поскольку плечи схемы идентичны, ток источника делится пополам, и ток стока ![]() . Передаточная проводимость

. Передаточная проводимость

![]() .

.

Коэффициенты усиления дифференциальной составляющей сигнала

![]()

Коэффициент усиления синфазной составляющей

Коэффициент ослабления синфазной составляющей

Рассмотренный пример показывает, что для увеличения ![]() следует использовать источники тока с большим внутренним сопротивлением.

следует использовать источники тока с большим внутренним сопротивлением.

Схема простейшего дифференциального усилителя на МОП-транзисторах показана на рис. 4.2.4.

Рис. 4.2.4

Вместо источника тока, обеспечивающего смещение рабочих точек транзисторов, в схеме на рис. 4.2.4 включен резистор  . Его величину можно найти из уравнений

. Его величину можно найти из уравнений

,

,

.

.

Коэффициенты усиления дифференциального и синфазного сигналов определяются выражениями (4.2.4) и (4.2.6). В формуле (4.2.6)  .

.

Существенный недостаток дифференциального усилителя на рис. 4.2.4 заключается в том, что резистор  определяет одновременно режим транзисторов по постоянному току и коэффициент ослабления синфазного сигнала. Поэтому получить большую величину

определяет одновременно режим транзисторов по постоянному току и коэффициент ослабления синфазного сигнала. Поэтому получить большую величину ![]() в таком усилителе невозможно.

в таком усилителе невозможно.

Значительно большее ослабление синфазного сигнала можно получить, включив вместо резистора  отражатель тока на транзисторах VT3 и VT4 (рис. 4.2.5).

отражатель тока на транзисторах VT3 и VT4 (рис. 4.2.5).

Рис. 4.2.5

Выходное сопротивление отражателя тока определяется сопротивлением канала транзистора VT4, находящегося в режиме насыщения. Выходной ток регулируется резистором  . Его величину можно найти из уравнений

. Его величину можно найти из уравнений

.

.

.

.

Постоянные составляющие токов и напряжений находятся так же, как и в схеме на рис. 4.2.4.

Включение отражателя тока в схеме на рис. 4.2.5 позволяет значительно увеличить коэффициент ослабления синфазного сигнала. Однако коэффициент усиления дифференциального сигнала остается прежним. Как следует из (4.2.4), его величина зависит от сопротивления ![]() и удельной проводимости МОП-транзистора

и удельной проводимости МОП-транзистора ![]() . Увеличивать сопротивления резисторов нежелательно, т.к. резисторы большого номинала занимают на кристалле интегральной схемы слишком большую площадь.

. Увеличивать сопротивления резисторов нежелательно, т.к. резисторы большого номинала занимают на кристалле интегральной схемы слишком большую площадь.

Эффективный способ увеличения коэффициента усиления дифференциальной составляющей – включение в цепи стоков транзисторов VT1 и VT2 отражателя тока на p-канальных транзисторах VT5 и VT6 (рис. 4.2.6). Такую схему называют усилителем с динамической (активной) нагрузкой.

Ток стока транзистора VT1 является управляющим для VT5. Если транзисторы VT5 и VT6 имеют одинаковые параметры, их токи равны:

![]()

Выходные характеристики МОП-транзисторов на участке, соответствующем режиму насыщения, имеют небольшой наклон. Поэтому для переменных составляющих токов каналы транзисторов VT5 и VT6 эквивалентны резисторам, имеющим большое сопротивление. Это позволяет увеличить коэффициент усиления дифференциальной составляющей и одновременно сэкономить площадь кристалла, т.к. отражатель тока занимает меньше места, чем высокоомные резисторы.

Следует помнить, что выходное сопротивление такого усилителя велико, поэтому и нагрузка должна иметь большое сопротивление, иначе усиление будет существенно ослаблено.

Рис. 4.2.6

Включение отражателя тока в цепи стоков транзисторов, образующих дифференциальную пару, обеспечивает еще одно преимущество. Поскольку проводимости каналов транзисторов различны, переменные составляющие токов VT2 и VT6 направлены встречно, поэтому выходной ток усилителя с активной нагрузкой в два раза больше, чем выходной ток схемы на рис. 4.2.5:

![]()

Таким образом, использование активной нагрузки позволяет исключить потерю усиления при несимметричном выходе.

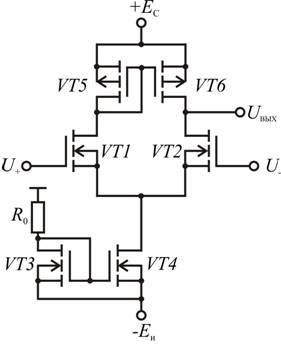

Другой вариант дифференциального усилителя с динамической нагрузкой показан на рис. 4.2.7. Здесь транзисторы имеют другой тип проводимости: дифференциальная пара реализована на p-канальных транзисторах VT1 и VT2, а нагрузка – на n-канальных транзисторах VT5 и VT6.

Рис 4.2.7

В схеме на рис. 4.2.7 режим транзисторов по постоянному току задается источником тока ![]() .

.